|

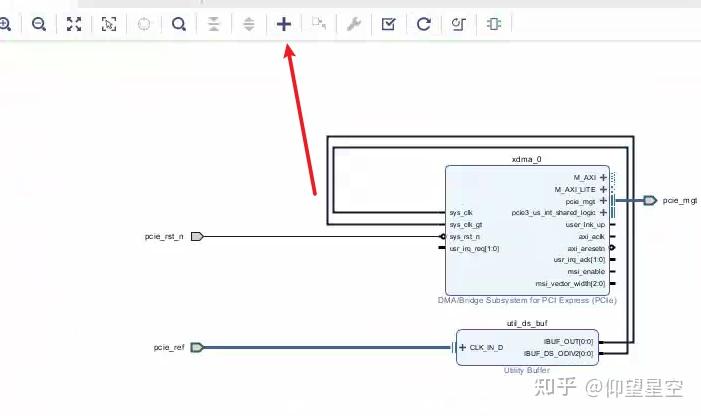

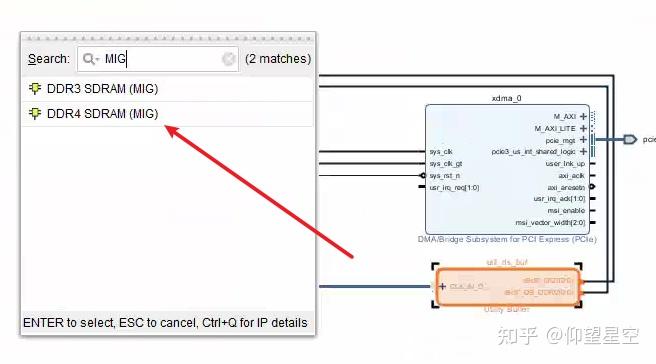

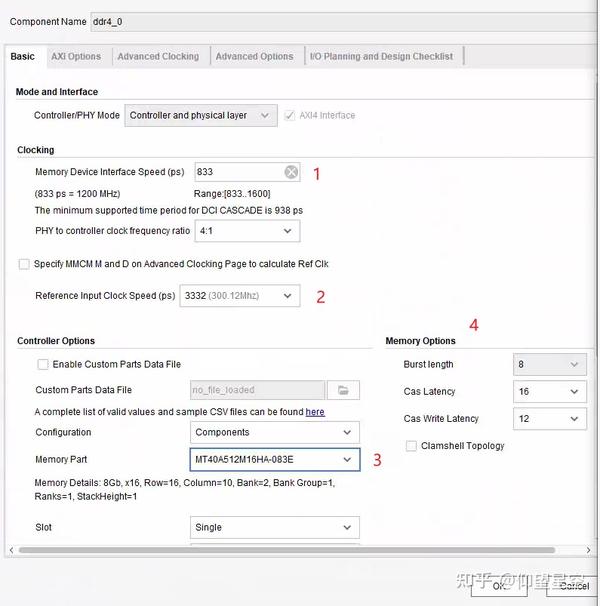

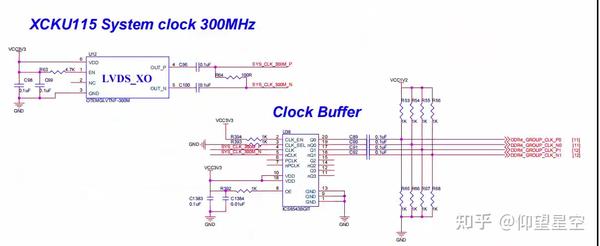

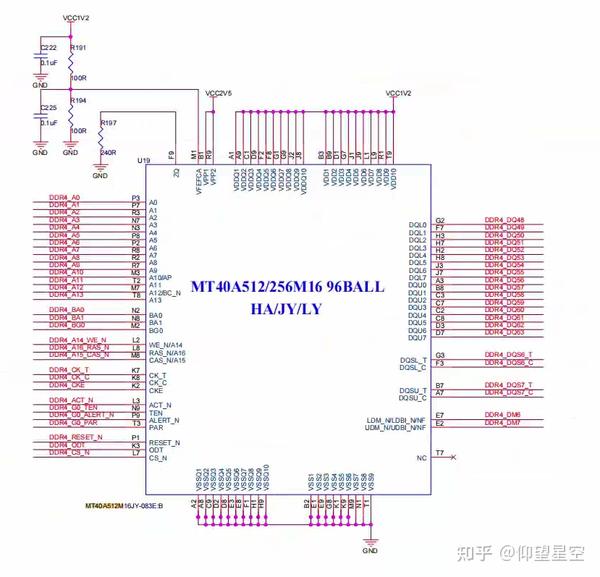

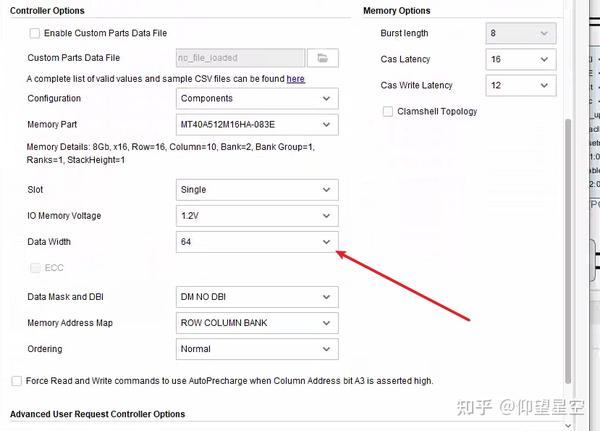

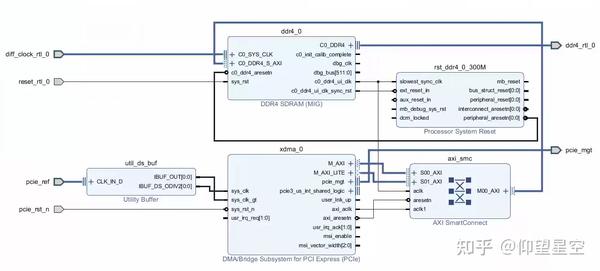

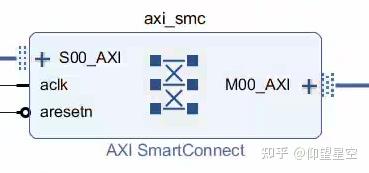

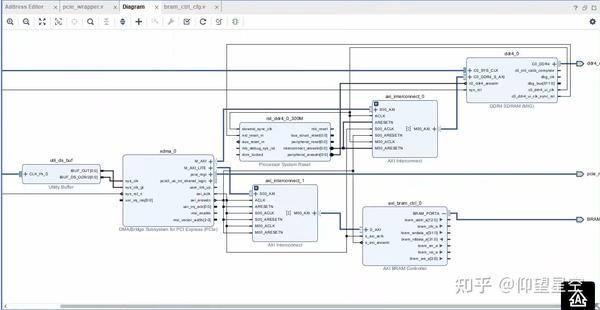

二、MIG的配置 这里需要接板卡上的DDR,如果相接BRAM,这里可以跳过。 MIG(Memory Device interface speed)本质是一个内存控制器,IP核的输出接口和内存相连。   根据实际型号进行选择即可。  (1) Memory Device interface speed 表示的是外部时钟频率1.2G,所以它的数据传输速率为2.4G,带宽为2.4G×64/8 = 19.2GB (2) 参考时钟  根据板卡的实际情况进行选择。 (3) DDR的型号  根据板卡的实际型号进行选择即可。 (4)这里还不是很清晰要怎么选择  选择64位位宽,这就是上面速率计算的原理。 其它栏目的选项直接默认即可。 生成MIG IP后,分别点:  完成后大概是这个样子:  这里多了两个IP,一个是asi_smc,另一个是rst_ddr4_0_300M 给位宽转换提供足够的时间,与AXI_interconnect IP功能相似,后续的文章不再使用它,换成AXI_interconnect IP。这里点开IP,把时钟改成1个。  2. rst_ddr4_0_300M Xilinx处理器系统复位模块允许客户通过设置某些参数来启用/禁用功能,从而根据自己的应用来定制设计。 想详细了解的可以参考下面的文章(这个IP不需要做任何的修改): [color=inherit !important]Xilinx IP解析之Processor System Reset v5.0blog.csdn.net/weixin_42837669/article/details/116853566

修改axi_smc后的,Diagram如下:

|