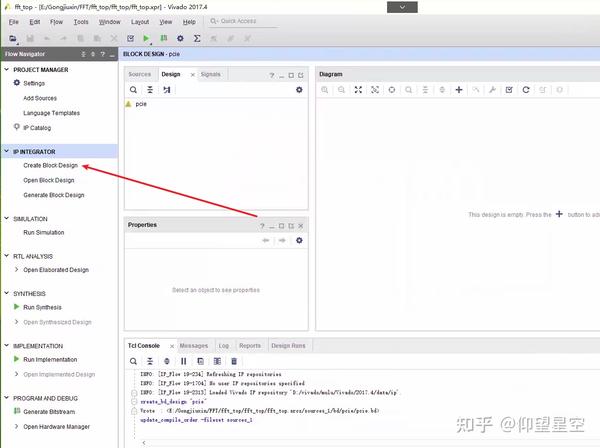

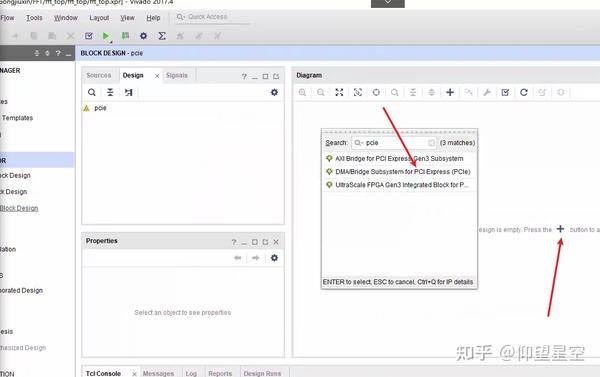

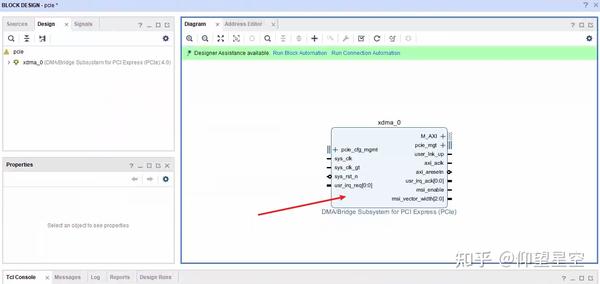

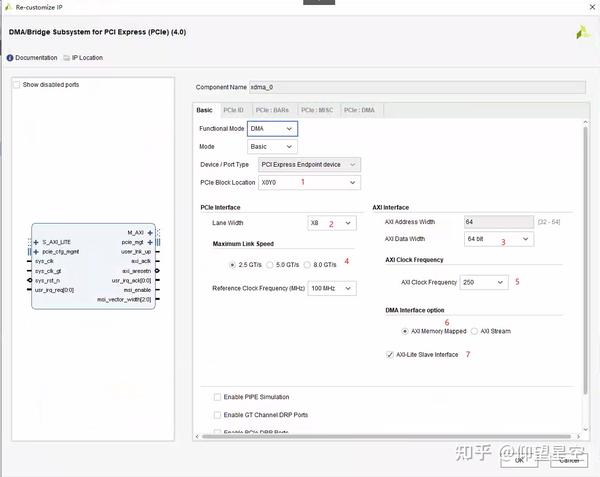

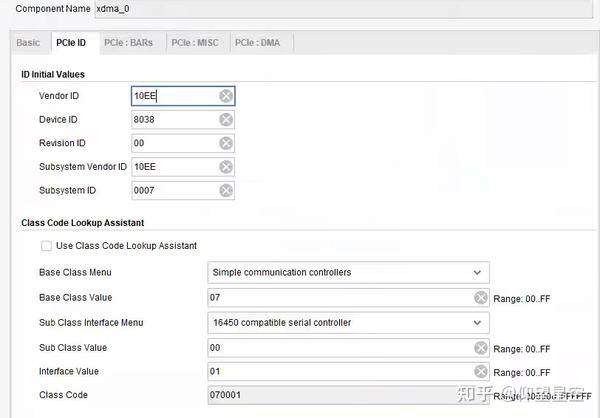

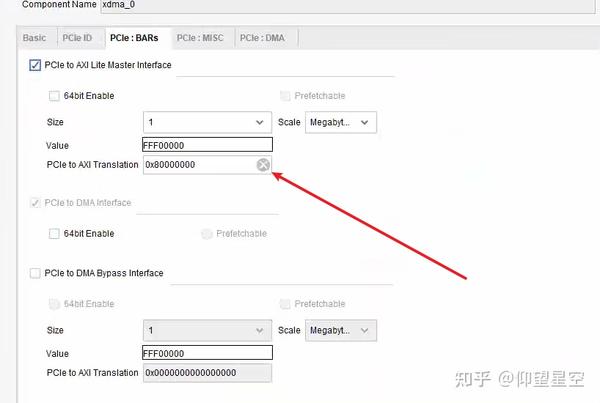

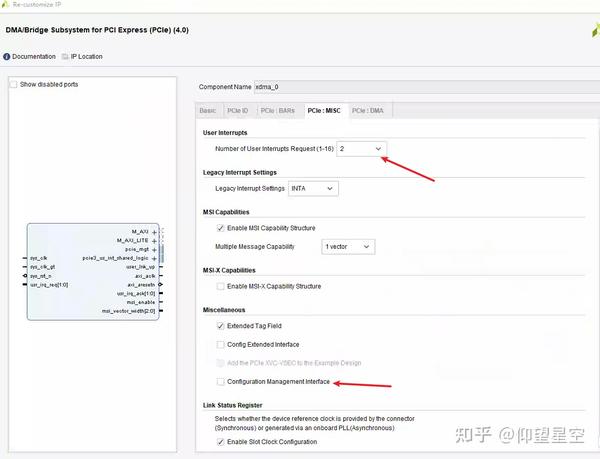

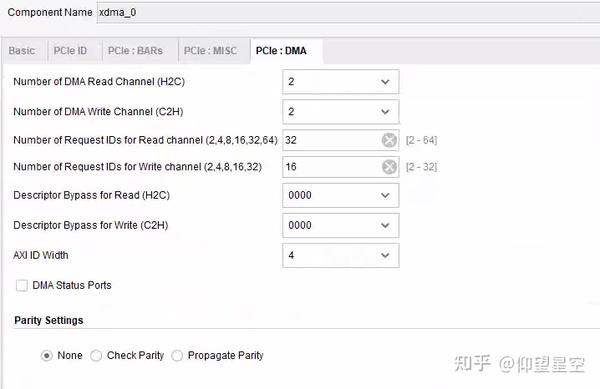

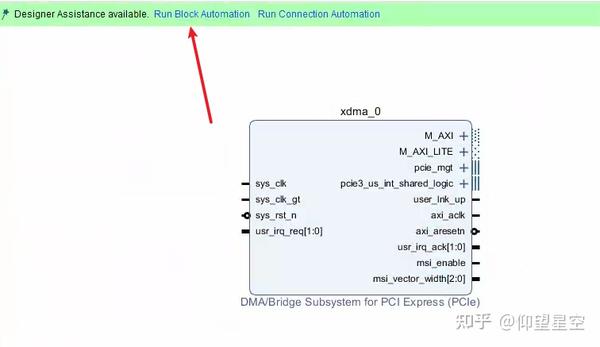

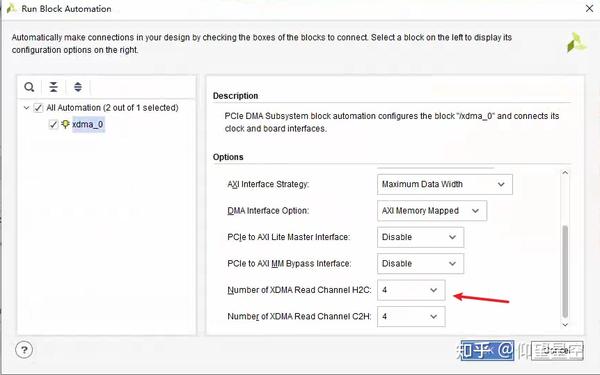

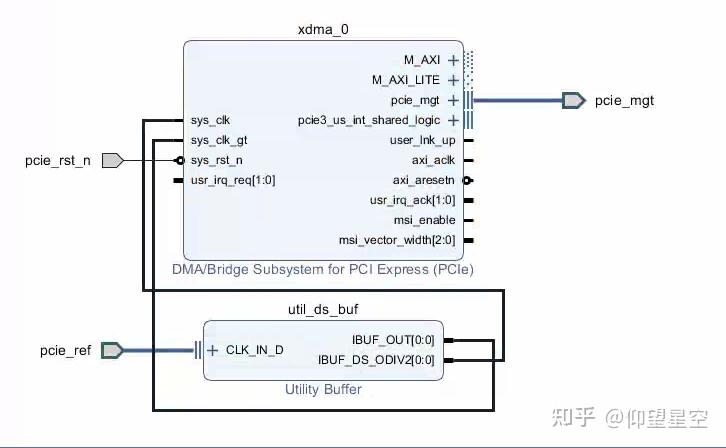

一、XDMA配置 2. 添加PCIE的IP  选择这个IP对应的用户接口为AXI4或者AXI4-stream。 3. 双击IP,进行配置  4. IP配置  参数: (1) PCIe Block Location 选择PCIe所在quad,该选择会生成特定的引脚和区域约束文件和引脚分配,有的FPGA芯片有多个PCIe location,在选择芯片的时候也可以看到。 (2) Lane Width 选择用多少通道进行传输,下面是PCIe理论传输速度表格:  (3)AXI data Width AXI主要用于传输数据,传输带宽64或128可选。 (4)Maximum Link Frequency 每个传输通道的最大速度 (5) AXI Clock Frequency 选择AXI参考时钟,根据位宽的不同,时钟是固定的。 (6)DMA Interface option 接口选择AXI (7)AXI4-Lite Slave 可选,用来将XDMA 内部寄存器开放给用户逻辑,用户逻辑可以通过此接口访问 XDMA内部寄存器,不会映射到BAR。我这里没有选择。  PCIe ID不需要更改。  (1)PCIE to AXI Lite Master Interface 主机一侧通过PCIE 来访问用户逻辑侧寄存器或者其他AXI4-Lite 总线设备。 (2)size 选择1M,可以根据实际需要大小进行配置。 (3) PCIE to AXI Translation 通常情况下,主机侧PCIE BAR 地址与用户逻辑侧地址是不一样的,这个设置就是进行BAR 地址到AXI 地址的转换,比如主机一侧 BAR 地址为0,IP 里面转换设置为 0x80000000,则主机访问 BAR 地址 0 转换到AXI LIte 总线地址就是0x80000000。  上面这页是DMA中断的配置,共提供16条中断线。 Legacy Interrupt:传统中断,非MSI中断,PCI设备使用INTx中断请求的方式与电平触发类似,而MSI/MSI-X中断请求的方式与边沿触发方式类似。当PCI设备的INTx信号有效时,PCIe桥将该信号转换为Assert_INTX消息报文,当这些INTx信号无效时,PCIe桥将该信号转换为Deassert_INTx中断信号。 注意:MSI 中断和 MSI-X 中断只能选择一个,否则会报错,如果选择了 MSI 中断,则可以选择 Legacy 中断,如 果选择了 MSI-X 中断,那么 MSI 必须取消选择,同时Legacy 也必须选择None。此 IP 对于7 系列设置有这个问题,如果使用Ultrascale 系列,则可以全部选择。  (1) Number of DMA Read Channel( H2C)& Number of DMA Write Channel(C2H) 对于PCIE2.0 来说最大只能选择 2,也就是 XDMA 可以提供最多两个独立的写通道和两个独立的读通道, 独立的通道对于实际应用中 有很大的作用,在带宽允许的前提前,一个PCIE 可以实现多种不同的传输功能,并且互不影响。 注意:多通道时在AXI Stream模式下影响很明显,在AXI Stream模式下选择多通道,可以连接不同的数据源。在AXI Memory Mapped模式下影响不大。 (2)Number of Request IDs for Read (Write) channel 这个是每个通道设置允许最大的 ID 数量,按照默认即可。   这个位置可能会自己更改,我们改成和XDMA IP核相同的配置即可。下图1、2、3分别代表PCIe的复位、时钟、接口,可以通过双击端口进行名字的修改。  至此,XDMA配置完毕。

|